# Low-Voltage Low-Power High dB-Linear CMOS Exponential Function Generator using Highly-Linear V-I Converter

Quoc-Hoang Duong

Information & Communication

University

58-4 Hwaam-Dong, Yuseong-gu,

Daejeon, South Korea

Tel. (82-42) 866 6184

Hoang@icu.ac.kr

Trung-Kien Nguyen

Information & Communication

University

58-4 Hwaam-Dong, Yuseong-gu,

Daejeon, South Korea

Tel. (82-42) 866 6203

ntkien@icu.ac.kr

Sang-Gug Lee

Information & Communication

University

58-4 Hwaam-Dong, Yuseong-gu,

Daejeon, South Korea

Tel. (82-42) 866 6133

sglee@icu.ac.kr

#### **ABSTRACT**

A CMOS voltage-to-current converter with exponential characteristic is presented in this paper. The concept of Taylor series expansion is used for realizing the exponential characteristic. The proposed exponential V-I converter is composed of a current-to-current squarer and a linear V-I converter with the use of linearization technique. Based on a 0.25  $\mu m$  CMOS process, simulations show a 23 dB of linear-output current range and the linearity within 20 dB with error less than  $\pm$  0.5dB is achieved. The total power consumption is below 0.2 mW with 1.25 V supply voltage. The proposed circuit can be used for the design of an extremely low-voltage low-power variable gain amplifier (VGA).

# Categories and Subject Descriptors

Architecture, Circuits, and Technology

Analog, MEMS and Mixed Signal Electronics

# **General Terms**

Design

#### Keywords

Exponential V-I converter, dB-linear, VGA

#### 1. INTRODUCTION

Low-voltage low-power VLSI circuits are of particular interest in the field of microelectronics. The demands for low voltage systems are driven by the factors of technology, design, and market. With the reduction of power supply voltage, many of the existing CMOS analog building blocks, designed to operate with higher supply voltages, will lose a significant amount of operating range and need to be reconsidered.

With advances in CMOS digital signal processing technique, CMOS became a main fabrication process for analog and mixed signal processing circuitry. The exponential V-I converter is an

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. to copy otherwise, or republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee. *ISLPED '03*, August 25–27, 2003, Seoul, Korea.

Copyright 2003 ACM 1-58113-682-X/03/0008...\$5.00.

important component for the implementation of VGA and automatic gain control amplifier (AGC) which are widely used in analog signal processing such as in hearing aids, disk drive, and telecommunication applications [1,2]. Unfortunately, there is no intrinsic logarithmic MOS device that operates in saturation region which helps to design dB-linear V-I converters. Although CMOS has exponential characteristics in weak inversion, for some high speed design, the circuit could be too slow.

The exponential function can be easily achieved in bipolar technology, however, bipolar techniques for AGC, VGA are not compatible for monolithic CMOS-based analog and mixed-signal circuits. On the other hand, the BiCMOS technology may not provide a cost-effective design solution.

One method to generate the exponential characteristics is using the "pseudo-exponential" function [2,3]. Alternatively, the Taylor series expansion concept can also be used for the implementation of the exponential characteristic. By applying the Taylor concept, a linear-logarithmic function can be obtained by using two building blocks; a linear V-I converter and a V-I squarer to realize the first-order and the second-order of the Taylor's polynomial as in [4]. However, for low-voltage applications, the linear V-I converter has significant drawback due to the reduction of the linear output current range [5]. Furthermore, the V-I squarer in [4], since it is composed of two identical V-I converters above, provides less linear-output current range and consumes higher power.

To overcome these difficulties, this paper proposes a new approach that uses two building blocks to achieve the exponential function. A low-voltage low-power current-to-current converter [6] is used instead of a voltage-to-current squarer as in [4] such that the power consumption of the overall circuit is reduced extremely, and a linear V-I converter [5] with the application of linearization technique such that it can operate with extremely low supply voltage.

# 2. BASIC PRINCIPLE AND PROPOSED FUNCTIONAL BLOCK DIAGRAM

According to the Taylor's series expansion, a general exponential function can be expressed as

$$\exp(ax) = 1 + \frac{a}{1!}x + \frac{a^2}{2!}x^2 + \dots + \frac{a^n}{n!}x^n + \dots$$

(1)

where a and x are the coefficient and the independent variable, respectively. Obviously, if  $a \ge 1$  and  $|x| \ge 1$  the exponential function cannot be implemented by a low-order polynomial. The exponential function can be approximated with small deviation by

eliminating the higher order terms if  $|ax| \ll 1$ . By neglecting the terms higher than second-order in Eq. 1, the approximated equation can be given as.

$$\exp(ax) \cong 1 + \frac{a}{1!}x + \frac{a^2}{2!}x^2 \tag{2}$$

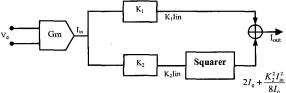

A new functional block diagram to realize the approximated Taylor's polynomial is given in Fig. 1. The second-order polynomial is synthesized by combining a low-voltage low-power V-I converter with linearization technique and a current squarer [5].

Figure 1: Proposed functional block diagram.

In Fig. 1, the output current  $(I_{in})$  of V-I linear converter is multiplied by  $K_1$  and  $K_2$  to generate the two currents  $K_1I_{in}$  and  $K_2I_{in}$  respectively. The  $K_2I_{in}$  signal goes through the current squarer, which has the transfer function as shown in Eq. 7, and the output of the current squarer is added with  $K_1I_{in}$  to form output current like in Eq. (2).

From Fig. 1, the output current as an exponential function is given as

$$I_{out} = 2I_0 + K_1 I_{in} + \frac{K_2^2 I_{in}^2}{8I_0}$$

$$= 2I_0 \left( 1 + K_1 \frac{I_{in}}{2I_0} + \frac{K_2^2 I_{in}^2}{16I_0^2} \right)$$

(3)

In Eq. (3),  $I_0$  represents the bias current of the current squarer [7]. To satisfy the condition of exponential function as in Eq. 2. From Eq. (2) and (3) the coefficient a and the independent variable x, have to satisfy the following condition

$$\frac{a^2}{2!} = \frac{(K_1/2I_0)^2}{2!} = \frac{K_2^2}{16I_0^2}$$

(4)

Then

$$\frac{K_2}{K_1} = \sqrt{2}$$

and  $a = \frac{K_1}{2I_0}$  (5)

From Eq. 5, the exponential characteristic can be easily obtained by proper setting of the multiplying factors  $K_1$ , and  $K_2$ . The multipliers can be easily implemented using current mirrors such that the exponential function depends only on process parameters. While in [4], three coefficients have to be adjusted.

#### 3. V-I LINEAR CONVERTER DESIGN

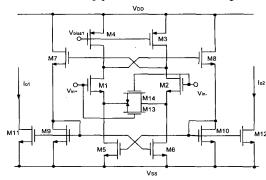

The V-I linear converter is shown in Fig. 2. Typically, the input swing of a differential amplifier is limited by threshold voltage of the core transistors and the excess voltage of the current sinks or sources. This results in a narrow window for differential-input voltage swing with low voltage applications.

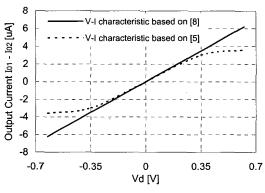

Fig. 2 shows the V-I linear converter that is used in this work [7]. The V-I converter shown in Fig. 2 combines the two previously reported linearization techniques: source degeneration using MOS transistors  $M_{13}$  and  $M_{14}$  [8], and class-AB linearization [9]. This circuit provides rail-to-rail differential input range. Fig. 3 shows the comparison of the V-I converter performance based on [5] and the circuit shown in Fig. 2.

Figure 2: The proposed highly linear V-I converter

Figure 3: Comparison of V-I converter performance based on [8] and the circuit shown in Fig. 2.

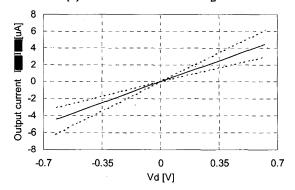

Figure 4: The V-I characteristic of the V-I converter shown in Fig. 2 for various  $V_{\rm biast}$ .

As can be seen from Fig. 3, the addition of the degeneration transistors  $M_{13}$  and  $M_{14}$  in Fig. 2 leads to almost perfectly linear V-I characteristic. In Fig. 2, a fixed transconductance can be obtained by controlling the bias voltage  $V_{\text{bias}1}$  of the load

transistors  $M_3$  and  $M_4$ . Fig. 4 shows the V-I characteristic of the circuit shown in Fig. 2 for various  $V_{bias1}$ . In Fig.4, the V-I characteristic stays linear for various slopes.

The output current  $I_{o1}$  -  $I_{02}$  is a linear function of the differential input voltage  $V_d$  where  $V_d = V_{in+}$  -  $V_{in-}$  as shown in Fig. 2.

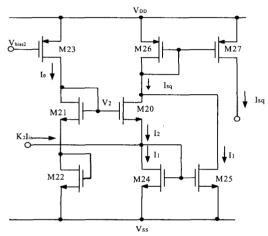

# 4. CURRENT SQUARING CIRCUIT

The current squaring circuit adopted from [6], which consumes extremely low power, is shown in Fig. 5. It can be shown that, in Fig. 5, the output current  $I_{sq}$  is given by [6]

$$I_{sq} = 2I_0 + \frac{K_2^2 I_{in}^2}{8I_0} \tag{7}$$

where  $I_0$  is the bias current as shown in Fig. 5.

As  $V_{bias2}$  in Fig.5 varies, the  $I_0$  changes such that the constant  $I_0$  in Eq. 3 is modified, leading to the modification of the overall V-I dB-linear characteristic.

Figure 5: The current squaring circuit [6].

In Fig.5, biasing the circuit with a current source has the additional advantage of making the transfer function independent of process parameters and operating temperature. In order to keep all devices in the ON state the input current must be restricted within the range  $\left|K_2I_{in}\right| < 4I_0$ .

#### 5. SIMULATION RESULTS

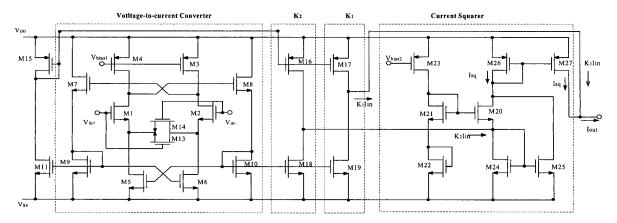

Fig. 8 shows the complete circuit of V-I exponential converter, which represents the circuit implementation of the proposed block diagram shown in Fig. 1.

In Fig. 8, four transistors  $(M_{11}, M_{19}, M_{15},$  and  $M_{17})$  form a current multiplier by a factor of  $K_1$ , and other four transistors  $(M_{11}, M_{18}, M_{15},$  and  $M_{16})$  form a current multiplier by a factor of K.

In Fig. 8, for a given value of  $V_{bias2}$ , the corresponding current  $I_0$  is defined. The input current  $I_{in}$  in Eq.(3), in order to satisfy the condition |ax| < 1 in Eq.(2), should satisfies the condition  $|K_1I_{in}| < 2I_0$ . Otherwise, the deviation of the approximated Eq.(2) from Eq.(1) will be increased. The bias voltage  $V_{bias1}$  can be adjusted to

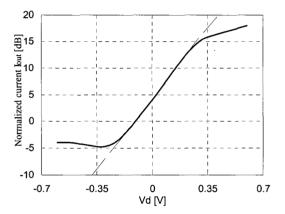

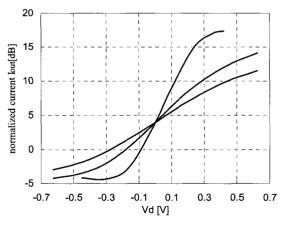

get the I-V curve that satisfies  $|K_1I_{in}| = 2I_0$  at  $|V_d| = V_{DD}/2$ . In this case, overall input voltage swing is from  $-V_{DD}/2$  to  $+V_{DD}/2$ , and 14 dB-linear output current could be obtained. Adjusting  $V_{bias1}$  for higher value of  $I_{in}$  can lead to higher range of dB-linear output current. However, the range of input voltage swing is reduced. The performance of normalized-dB V-I characteristic with  $V_{bias1} = 0.62$  V is shown in Fig. 6, in which 22 dB-linear output current range is achieved, and 18 dB-linear of linear performance with error less than  $\pm 0.5$  dB over the range of  $V_d$  from -0.25V to 0.3V. Fig. 7 shows the normalized dB-linear V-I characteristics of the complete exponential V-I converter in Fig. 8 for various Vbias1.

As summarized in table 1, higher dB-linear range can be achieved with sacrificing in the input voltage swing. As can be seen in Table. 1, a 20 dB-linear output current with error less than  $\pm 0.5$  dB can be obtained with  $V_{\text{bias}1}=0.56$  V. The dB-linear range can be programmed by adjusting  $V_{\text{bias}2}$  and  $V_{\text{bias}2}$ .

Figure 6: The normalized dB-linear performance of the exponential V-I converter at  $V_{\rm bias1}=0.62~V_{\rm \cdot}$

Figure 7: The normalized dB-linear performance with different  $V_{\text{bias}1}$ .

Figure 8: The complete schematic of the proposed exponential V-I converter.

Table 1. The summary of the performance of the proposed V-I converter

| V <sub>bias1</sub> [V]                                           | 0.56       | 0.6       | 0.65      | 0.7        | 0.8       |

|------------------------------------------------------------------|------------|-----------|-----------|------------|-----------|

| Output current range Iout [dB]                                   | 23         | 22.5      | 21        | 18         | 14        |

| Output current range $I_{out}$ with error less than $\pm$ 0. 5dB | 20         | 19        | 16        | 13         | 12        |

| Input voltage swing V <sub>d</sub> [V]                           | -0.12÷0.15 | -0.2÷0.25 | -0.25÷0.3 | -0.35÷0.35 | -0.4÷0.45 |

# 6. CONCLUSIONS

A novel approximation function to realize the exponential relation which is found in almost all VGA circuits is presented with programmable dB-linear range for extremely low-voltage low-power applications. The average power consumption is less than 0.2 mW at 1.25 V supply voltage. The proposed V-I converter can achieve 20 dB-linear output current with the error less than  $\pm 0.5$  dB. The proposed circuit could be used in the design of an extremely low-voltage and low-power VGA.

### 7. REFERENCES

- [1] G. S. Sahota and C.J Persico, "High Dynamic Range Variable-Gain Amplifier for CDMA Wireless Application," Proc. Of 1997 IEEE International Solid-State Circuits Conference, pp.374-375, 1997.

- [2] R. Harijani, "A Low-power CMOS VGA for 50 Mb/s Disk Drive Read Channels," *IEEE Transactions on Circuits and Systems-II: Analog and Digital Signal Processing*, vol. 42, no. 6, pp. 370-376, June, 1995.

- [3] A. Motanemd, C. Hwang and M. Ismail, "CMOS exponential current-to-voltage converter", *Electronics Letters*, vol. 33, no. 12, pp. 998-1000, 5<sup>th</sup> June, 1997.

- [4] Lin, C., Pimenta, T., and Ismail, M., "Universal exponential function implementation using highly-linear CMOS V-I converters for dB-linear (AGC) application". Proc. 1998 IEEE Midwest symp. Circuits and Systems, 1999, pp. 360-363.

- [5] C.-H. Lin, M. Ismail and T. Pimenta "A 1.2 V Micropower CMOS Class AB V-I converter for VLSI Cells Library Design," Proc. Of 1998 IEEE Midwest Symposium on Circuit and Systems, September, 1998.

- [6] K. Bult and H. Wallinga, "A Class of Analog CMOS Circuits Based on the Square-Law Characteristic of an MOS Transistor in Saturation," *IEEE J. of Solid-State Circuits*, vol. sc-22, no. 3, June 1987.

- [7] Trung-Kien Nguyen and Sang-Gug Lee, "Low-voltage low-power CMOS transconductance amplifier with rail-to-rail differential input range," this paper is submitted to this conference.

- [8] F. Krummenacher and N. Joehl, "A 4-MHz CMOS continuous-time filter with on-chip automatic tunning," *IEEE J.Solid-State Circuit*, vol.23, pp. 750-758, June 1988.

- [9] K. Ko-Chi and L. Adrian, "A linear MOS Transconductor Using Source Degeneration and Adaptive Biasing," IEEE Trans. Circuits Syst, vol. 48, pp. 937-943, October 2001.

- [10] A. Nedungadi and T. R. Viswanathan, "Design of linear CMOS transconductance elements," *IEEE Trans. Circuits Syst.*, vol. CAS-31, pp.891-894, Oct. 1984.

# 8. ACKNOWLEDGEMENT

The work is supported by Digital Media Lab which is funded by Ministry of Information and Communication; Korea.