## Compact low-power high-slew-rate buffer for LCD driver applications

H.-B. Le, X.-D. Do and S.-G. Lee

A very compact, rail-to-rail, low-power, high-speed buffer amplifier for LCD driver applications is proposed. A slew-rate enhancement technique based on a dynamic current bias scheme is adopted, and a high slew-rate is obtained without increasing the quiescent current. The buffer amplifier uses a small number of transistors and enables very small active layout area. The proposed buffer amplifier is suitable for both low- and high-voltage LCD driver applications.

Introduction: As liquid-crystal displays (LCDs) approach high resolution, high quality, and physically large panel size, the design of output buffer amplifiers becomes more challenging. More specifically, the buffer amplifier needs to be faster in order to deal with larger load capacitance and resistance and thereby achieve smaller settling time. In addition, hundreds or thousands of output buffer amplifiers are integrated into one driver IC, and the buffer should occupy a small die area and consume small static power. It also should provide a rail-to-rail voltage driving capability so that higher grey levels can be accommodated.

To reduce settling time, the slew-rate of the buffer amplifier should be increased, because the slewing time normally dominates the settling time in LCD applications. Several techniques have thus far been used to increase slew-rate without additional static power. Lu [1, 2] used additional comparators to sense the rising/falling edges of the input and then turn on push/pull transistors in the output stage to charge/discharge the output load. Yu and Wu [3] proposed a class B buffer in which a comparator is used in the negative feedback path to eliminate the static current in the output stage. Kim and Cho [4] adopted positive feedback loops to speed up the slew-rate of the proposed buffer when there is a voltage difference in the differential input. Choi et al. [5] developed an adaptive dynamic current biasing scheme to increase slew-rate without increasing the quiescent current. In this Letter we propose a very compact low-power high-speed rail-to-rail buffer amplifier using a slew-rate enhancement technique (SRET) based on the adaptive current biasing scheme [5].

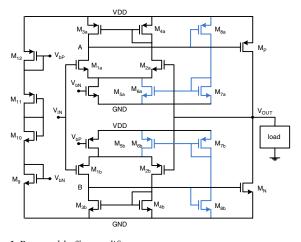

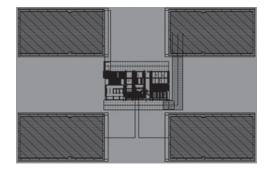

Fig. 1 Proposed buffer amplifier

Proposed buffer amplifier: Fig. 1 schematically illustrates the proposed buffer amplifier. To provide rail-to-rail driving capability, the buffer is composed of two complementary differential inputs with a commonsource push-pull output stage,  $M_{\rm N}/M_{\rm P}$ . The upper part,  $M_{\rm 1a}$ - $M_{\rm 5a}$ , with an NMOS input stage drives the output PMOS transistor,  $M_{\rm P}$ , for sourcing current. The lower part,  $M_{\rm 1b}$ - $M_{\rm 5b}$ , with an PMOS input stage drives the output NMOS transistor,  $M_{\rm N}$ , for sinking current. Transistors  $M_{\rm 6a/b}$ - $M_{\rm 8a/b}$  form the slew-rate enhancement circuits.  $M_{\rm 6a}$ - $M_{\rm 8a}$  in the upper part are responsible for rising slew enhancement while  $M_{\rm 6b}$ - $M_{\rm 8b}$  in the lower part are responsible for falling slew enhancement. In the steady state, where the input and output voltage are the same, the slew enhancement circuits should consume very small static current in order to save power. Accordingly,  $M_{\rm 8a/b}$  should be turned off during the steady state by biasing  $M_{\rm 3a/b}$ - $M_{\rm 4a/b}$  in the triode region so that the drain voltages of  $M_{\rm 3a}$ - $M_{\rm 4a}$  are close to VDD

and those of  $M_{3b}$ - $M_{4b}$  are close to GND. The gate-source and drain-source voltages of these transistors should satisfy the following conditions:

$$|V_{GS\_8a}| = |V_{DS\_3a}| = |V_{DS\_4a}| = |V_{GS\_4a}| < |V_{thp}|$$

(1)

$$V_{GS\_8b} = V_{DS\_3b} = V_{DS\_4b} = V_{GS\_4b} < V_{thn}$$

(2)

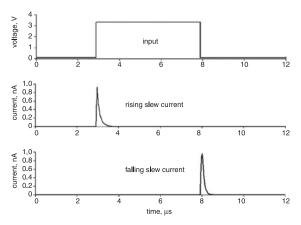

In the slewing condition, when a large low-to-high step signal appears at the input,  $V_{\rm IN}$ , all the tail current from  $M_{5a}$  flows through  $M_{3a}$ ; accordingly, the drain voltage of  $M_{3a}$ ,  $V_{\rm A}$ , decreases. Subsequently,  $M_{8a}$  turns on and provides additional current to the upper part input pair through the current mirror circuit,  $M_{6a}$ - $M_{7a}$ . Similarly, the falling slew detection circuit,  $M_{6b}$ - $M_{8b}$ , operates when a large high-to-low step signal appears at the input, providing more current to the lower part input pair. In summary, whenever a large step signal is applied to the input (slewing condition), additional current will be supplied to the input pair, providing more dynamic current, which in turn helps to increase the slew-rate of the proposed buffer amplifier. Fig. 2 shows the simulated transient currents flowing through the lower and upper part, respectively, during slewing period. The maximum dynamic currents are more than 900  $\mu$ A from the quiescent bias currents of less than 1  $\mu$ A.

Fig. 2 Simulated transient currents during slewing period

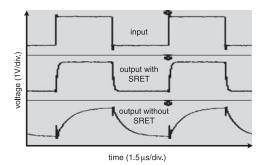

Fig. 3 Measured step responses of version\_01 chip with and without SRET

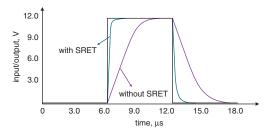

Experimental results: To verify the proposed slew-rate enhancement technique, two versions of the proposed buffer were designed in different processes. Version\_01 was designed and fabricated in a 0.18 µm CMOS process with a 3.3 V supply for low-voltage LCD driver applications, while version\_02 was designed and simulated in a 0.35 µm CMOS process with a 12.0 V supply for high-voltage LCD driver applications. Fig. 3 shows the measured step responses of version\_01 chip with and without the SRET for a step input of 0.1-3.2 V and 680 pF capacitive load. The SRET helps to increase the rising/falling slewrates roughly seven-fold (from 2.6/2.5 to  $18.0/18.5 \text{ V/}\mu\text{s}$ ). The rising/falling settling times within 0.2% of the final voltage are 0.45/  $0.40 \mu s$  when using the SRET and  $2.40/2.70 \mu s$  without using the SRET. Fig. 4 shows the simulated transient responses of the version\_02 chip with a step input of 0.1-11.9 V and 1.0 nF capacitive load. The rising/falling slew-rates are 25.0/23.0 and  $4.1/4.0 \text{ V/}\mu\text{s}$ for the proposed buffer with and without the SRET, respectively. The rising/falling settling times within 0.2% of the final voltage are 1.4/ 1.5  $\mu$ s with the SRET and 4.5/5.0  $\mu$ s without the SRET. The measured maximum offset voltage for the version\_01 chip is 3.5 mV, and within 90% of the input range, 0.15-3.15 V, the offset voltage is less than 1.0 mV. Fig. 5 shows the layout of the version\_01 chip. The chip occupies an active area of  $30\times60~\mu m$ . Table 1 presents a performance summary and comparisons with several published works. The proposed buffer shows the best performance.

Fig. 4 Simulated step responses of version\_02 chip with and without SRET

Fig. 5 Version\_01 chip layout

Table 1: Performance summary and comparisons

| Parameters                       | This work                |                           |              |                |              |             |            |

|----------------------------------|--------------------------|---------------------------|--------------|----------------|--------------|-------------|------------|

|                                  | Version_01<br>(measured) | Version_02<br>(simulated) | [1]          | [2]            | [3]          | [4]         | [5]        |

| Process                          | 0.18 µm                  | 0.35 μm HV                | 0.60 μm      | 0.35 μm        | 0.80 μm      | 0.35 μm     | 0.35 μm    |

| Supply<br>voltage<br>(V)         | 3.3                      | 12                        | 5            | 3.3            | 5            | 3.3         | 3.3        |

| Load                             | 680 pF                   | 1.0 nF                    | 680 pF       | 680 pF         | 600 pF       | 1.0 nF      | 20k/200 pF |

| Input/<br>output<br>range        | 0.1-3.2                  | 0.1-11.9                  | 0.15-4.0     | 0.14-3.09      | 1.0-5.0      | NA          | 0-3.3      |

| Slew-<br>rate +/<br>- (V/μs)     | 18.0/18.5                | 25.0/23.0                 | NA           | NA             | NA           | >10         | 8          |

| Max.<br>offset<br>(mV)           | 3.5                      | 3.6                       | 6            | NA             | 7            | 10          | NA         |

| Settling<br>time +/<br>- (μs)    | 0.45/0.40                | 1.4/1.5                   | 1.6/1.0      | 1.1/1.3        | 8.0/3.0      | NA          | 7.2/6.4    |

| Static<br>current<br>(µA)        | 0.3-1.3                  | 1.0 - 4.0                 | 30           | 4.5            | 24           | 1           | 5-6.5      |

| Chip size $(\mu m \times \mu m)$ | 30 × 60                  | NA                        | NA           | NA             | 230 × 140    | NA          | NA         |

| 1 5                              | Settling time at         | 0.2% of final v           | oltage; +/ - | : rising/falli | ng edge; HV: | high voltag | e          |

Conclusions: A very compact high-speed low-power buffer amplifier is presented. The proposed slew-rate enhancement technique helps to increase the speed of the buffer without additional static current. The number of transistors has been minimised thanks to the slew-rate enhancement technique, and the active area is very compact. The proposed buffer shows excellent performance in terms of speed, offset, power consumption, and chip size for both low and high voltage supplies, and thus has considerable potential for LCD drive applications.

Acknowledgment: This research was financially supported by the Ministry of Education, Science Technology (MEST) and Korea Institute for Advancement of Technology (KIAT) through the Human Resource Training Project for Regional Innovation.

© The Institution of Engineering and Technology 2010 13 August 2010

doi: 10.1049/el.2010.2236

One or more of the Figures in this Letter are available in colour online.

H.-B. Le, X.-D. Do and S.-G. Lee (Department of Electrical Engineering, Korea Advanced Institute of Science and Technology (KAIST), 119-Mujiro, Yuseong-gu, Daejeon, 305-732, Republic of Korea)

E-mail: binh@kaist.ac.kr

## References

- Lu, C.-W., and Lee, C.L.: 'A low power high speed class-AB buffer amplifier for flat panel display application', *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, 2002, 10, (2), pp. 163–168

Lu, C.-W., and Hsu, K.-J.: 'A high speed low power rail-to-rail column

- 2 Lu, C.-W., and Hsu, K.-J.: 'A high speed low power rail-to-rail column driver for AMLCD application', *IEEE J. Solid-State Circuits*, 2004, 39, (8), pp. 1313–1320

- 3 Yu, P.-C., and Wu, J.-C.: 'A class-B output buffer for flat-panel-display column driver', *IEEE J. Solid-State Circuits*, 1999, **34**, (1), pp. 116–119

- 4 Kim, S.-K., and Cho, G.-H.: 'Low power high-slew-rate CMOS buffer amplifier for flat panel display drivers', *Electron. Lett.*, 2006, 42, (4), pp. 214–215

- 5 Choi, J.-Y., Min, K.-Y., and Yoo, C.-S.: 'High-speed and low-power analog source driver for TFT-LCD using dynamic current biased operational amplifier', SID Symp. Dig., 2007, 38, (2), pp. 1647–1650